## **Solar Cells on CMOS Chips As Energy Harvesters**

— Integration and CMOS Compatibility

Jiwu Lu

## The graduation committee consists of:

Chairman: prof.dr.ir. A.J. Mouthaan University of Twente Secretary: prof.dr.ir. A.J. Mouthaan University of Twente Supervisor: prof.dr. J. Schmitz University of Twente Asst. Supervisor: dr. A.Y. Kovalgin University of Twente Referees: dr. K. Reimann NXP Semiconductors

dr. R. Vullers Holst Center

Members: prof.dr.ir. R.A.M. Wolters University of Twente

prof.dr.ir. J.W.M. Hilgenkamp University of Twente

prof.dr. F. Roozeboom Eindhoven University of

Technology

This research was supported by Dutch Technology Foundation STW (project "Plenty of room at the top" TET 6630) and carried out at the Semiconductor Components group, MESA+ Institute for Nanotechnology, University of Twente, The Netherlands.

Title: Solar Cells on CMOS Chips As Energy Harvesters

— Integration and CMOS Compatibility

Author: Jiwu Lu

ISBN: 978-90-365-3211-2

DOI: 10.3990/1.9789036532112

© 2011, Jiwu Lu All rights reserved

# SOLAR CELLS ON CMOS CHIPS AS ENERGY HARVESTERS — INTEGRATION AND CMOS COMPATIBILITY

## **DISSERTATION**

to obtain

the degree of doctor at the University of Twente,

on the authority of the rector magnificus,

prof.dr. H. Brinksma,

on account of the decision of the graduation committee,

to be publicly defended

on Wednesday, the 22<sup>nd</sup> of June at 12:45, 2011

by

Jiwu Lu

born on November 20<sup>th</sup>, 1977 in Hunan, China This dissertation is approved by :

Prof. Dr. Jurriaan Schmitz (supervisor)

Dr. A.Y. Kovalgin (assistant supervisor)

## **CONTENTS**

| CHAPTER 1. |        | INTRODUCTION                                         | 1  |

|------------|--------|------------------------------------------------------|----|

| 1.1        | WHY    | ENERGY HARVESTING?                                   | 1  |

| 1.2        | Requ   | IREMENTS FOR AN ENERGY HARVESTER                     | 4  |

|            | 1.2.1  | Power                                                | 4  |

|            | 1.2.2  | Size                                                 | 4  |

|            | 1.2.3  | Flexibility                                          | 5  |

|            | 1.2.4  | Challenge of CMOS compatible manufacturing           | 5  |

| 1.3        | Sour   | CES FOR ENERGY HARVESTING                            | 6  |

|            | 1.3.1  | Sunlight                                             | 6  |

|            | 1.3.2  | Mechanical Vibrations                                | 7  |

|            | 1.3.3  | Air flow                                             | 8  |

|            | 1.3.4  | Thermal Gradient                                     | 9  |

|            | 1.3.5  | Human Power                                          | 9  |

|            | 1.3.6  | Radiofrequency (RF) radiation                        | 10 |

|            | 1.3.7  | Radioisotope                                         | 11 |

| 1.4        | ADVA   | NTAGE OF A SOLAR CELL AS AN ENERGY HARVESTER         | 12 |

| 1.5        | OUTL   | INE OF THE THESIS                                    | 13 |

| CHAP       | TER 2. | VIBRATION BASED ENERGY HARVESTER                     | 14 |

| 2.1        | GENE   | RAL MODEL FOR VIBRATION CONVERSION                   | 14 |

| 2.2        |        | OF VIBRATION BASED ENERGY HARVESTER                  |    |

|            | 2.2.1  | Electromagnetic energy harvester (EM harvester)      |    |

| •          | 2.2.2  | Electrostatic energy harvester                       |    |

|            | 2.2.3  | Piezoelectric energy harvester                       |    |

| 2.3        |        | ELING OF AN INTEGRATED EM HARVESTER                  |    |

|            | 2.3.1  | Design of the new EM energy harvester                |    |

| 2.3.1      |        | Numerical Simulations                                |    |

|            | 2.3.3  | Discussion                                           |    |

| 2.4        |        | UENCY MATCH CHALLENGE                                |    |

| 2.5        |        | LUSIONS                                              |    |

| CHAPTER 3. |        | SOLAR CELLS ON TOP OF CMOS CHIPS AS ENERGY HARVESTER |    |

|            |        |                                                      |    |

| 3.1        |        | CE OF THE TECHNOLOGY                                 |    |

| 3.1.1      |        | Monolithic Integration                               |    |

| 3.1.2      |        | Solar cells selected as energy harvesters            |    |

|            | 3.1.3  | CMOS chips selected for monolithic integration       | 38 |

| 3.2 Passi  | VATION LAYERS FOR POST-PROCESSING                                          | 39     |

|------------|----------------------------------------------------------------------------|--------|

| 3.2.1      | Deposition of Passivation layers                                           | 40     |

| 3.2.2      | Electrical characterization                                                | 41     |

| 3.2.3      | Conclusions                                                                | 44     |

| 3.3 Sumi   | MARY                                                                       | 45     |

| CHAPTER 4. | A-SI SOLAR CELL INTEGRATION                                                | 46     |

| 4.1 A-SIS  | SOLAR CELL INTRODUCTION                                                    | 46     |

| 4.1.1      | Brief history                                                              | 46     |

| 4.1.2      | Cell structure                                                             | 47     |

| 4.1.3      | Advantages of a-Si monolithic integration for energy harvesting            | 48     |

| 4.1.4      | Extra challenge for the integration of a-Si solar cells compared to that o | f a-Si |

| photodi    | iodes                                                                      | 49     |

| 4.2 A-SIS  | SOLAR CELL INTEGRATION ON CMOS                                             | 50     |

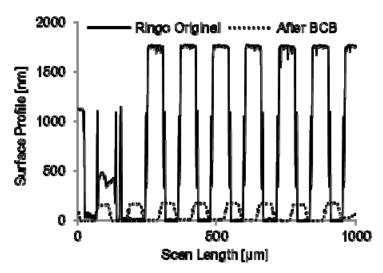

| 4.2.1      | Planarization of the chip surface                                          | 51     |

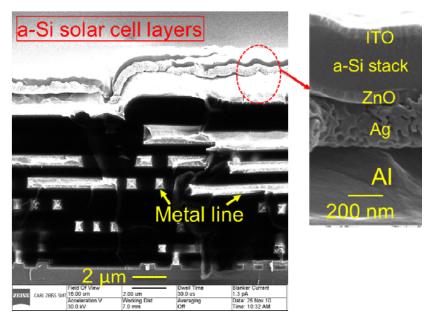

| 4.2.2      | Passivation layer deposition                                               | 52     |

| 4.2.3      | Solar cell deposition                                                      | 53     |

| 4.2.4      | Solar cell de-processing                                                   | 54     |

| 4.3 EXPE   | RIMENTAL RESULTS                                                           | 55     |

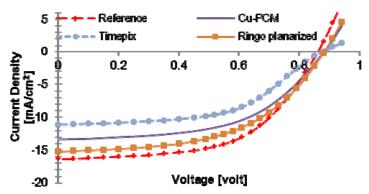

| 4.3.1      | PV cell functionality                                                      | 55     |

| 4.3.2      | Solar cell efficiency and yield                                            | 57     |

| 4.4 CMC    | OS COMPATIBILITY OF A-SI SOLAR CELL INTEGRATION                            | 59     |

| 4.4.1      | C-V and I-V measurements on the Cu-PCM chips                               | 59     |

| 4.4.2      | Functionality of a CMOS Ring Oscillator                                    | 61     |

| 4.4.3      | Functionality of the Timepix chip                                          | 61     |

| 4.5 Cond   | CLUSION                                                                    | 62     |

| CHAPTER 5. | CIGS SOLAR CELL INTEGRATION AS ENERGY HARVESTER                            | 63     |

| 5.1 INTRO  | DDUCTION TO CIGS SOLAR CELL                                                | 63     |

| 5.1.1      | Brief history                                                              | 63     |

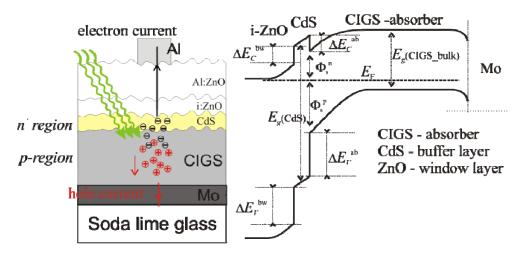

| 5.1.2      | Basic theory                                                               | 65     |

| 5.1.3      | Integrated CIGS solar cell as energy harvester                             | 67     |

| 5.2 THE (  | CIGS INTEGRATION CHALLENGE                                                 | 68     |

| 5.3 PROT   | OTYPE DESIGN AND EXPERIMENT                                                | 69     |

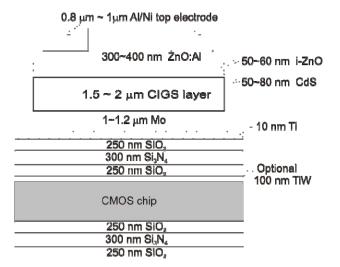

| 5.3.1      | Passivation layer deposition                                               | 70     |

| 5.3.2      | Solar cell deposition                                                      | 71     |

| 5.3.3      | De-processing of the solar cells                                           | 71     |

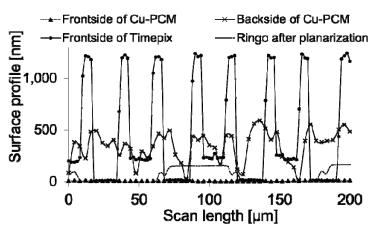

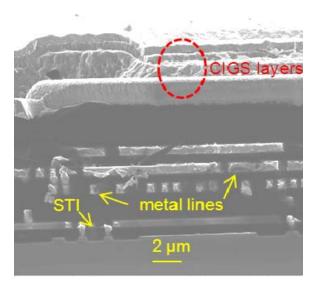

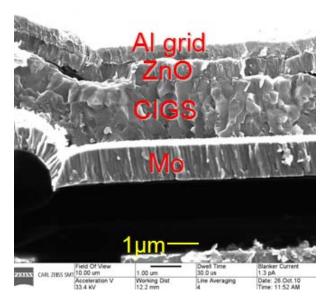

| 5.3.4      | Physical characteristics of CIGS solar cell on chip                        |        |

| 5.4 SOLA   | R CELL EXPERIMENTAL RESULTS                                                | 74     |

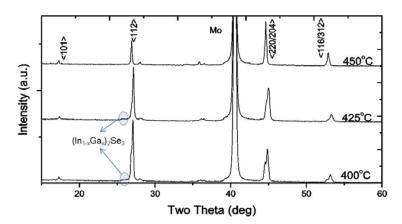

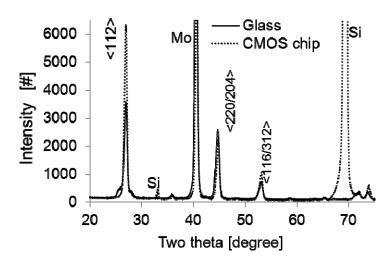

| 5.4.1      | Crystallinity and chemical composition of the CIGS layer                   | 74     |

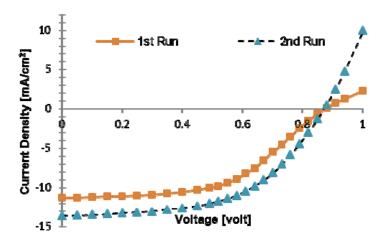

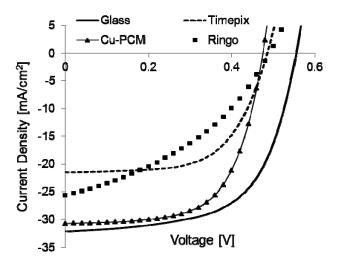

| 5.4.2        | Current-voltage behavior of the solar cells          | 76  |

|--------------|------------------------------------------------------|-----|

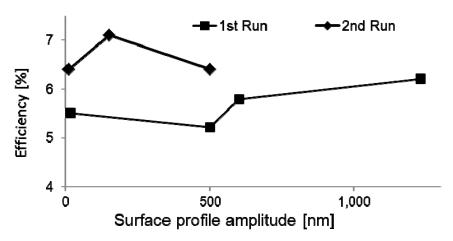

| 5.4.3        | Efficiency and yield                                 | 78  |

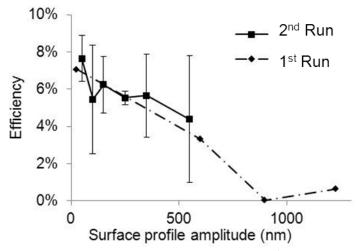

| 5.4.4        | Efficiency of PV cells versus chip topography        | 79  |

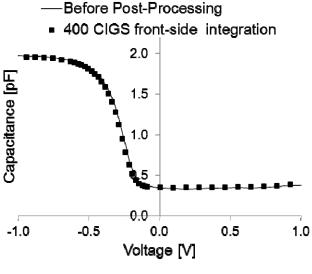

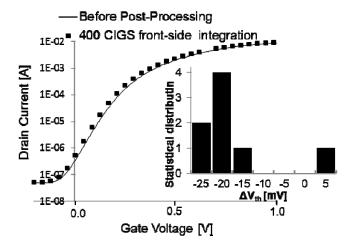

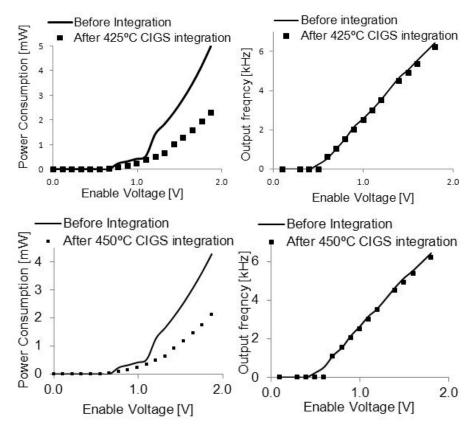

| 5.5 CMC      | OS CHIP PERFORMANCE AFTER THE SOLAR CELL INTEGRATION | 80  |

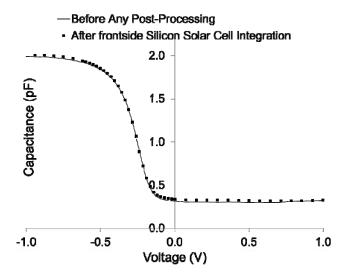

| 5.5.1        | C-V and I-V measurements on Cu-PCM devices           | 80  |

| 5.5.2        | Functionality of the Ringo chip                      | 82  |

| 5.5.3        | Functionality of Timepix chip                        | 83  |

| 5.6 Cond     | CLUSION                                              | 85  |

| CHAPTER 6.   | CONCLUSIONS AND RECOMMENDATIONS                      | 86  |

| 6.1 Cond     | CLUSIONS                                             | 86  |

| 6.1.1        | CMOS compatibility                                   | 86  |

| 6.1.2        | PV efficiency and yield on CMOS chips                | 88  |

| 6.1.3        | Comparison of technologies                           | 89  |

| 6.2 RECC     | MMENDATION                                           | 90  |

| CONCLUSIES   | EN AANBEVELINGEN                                     | 107 |

| LIST OF PUBL | ICATIONS                                             | 114 |

| ACKNOWI      | .EDGEMENT                                            | 115 |

## **Chapter 1. Introduction**

Energy scavenging - also known as Energy harvesting - has recently drawn huge interests in both academia and industry. The concept is to power microelectronic devices by gathering energy from the environment surrounding the device itself. It is a potential solution for powering various low power electronic devices for autonomous systems; that is, maintenance free systems. In this thesis we will propose a new approach to harvest energy in a microsystem.

## 1.1 Why energy harvesting?

Ubiquitous computing needs hundreds of working micro-electronic devices everywhere and whenever. Traditional power supplies cannot meet the energy needs of such systems. However, the development of low-power IC technology has reach to such a level that energy harvesting from the environment surrounding the electronic device needs no longer be a dream.

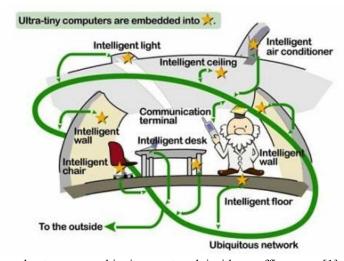

Fig. 1.1 shows the envisaged ubiquitous computing system first proposed by Dr. Mark Weiser [2, 3]. He stated that: "I call this future world "ubiquitous computing"; such a world will "Provide hundreds of wireless computing devices per person per office, of all scales (from 1" displays to wall sized)."

Fig. 1.1. Envisaged autonomous ubiquitous network inside an office room [1].

"A computer so imbedded, so fitting, so natural, that we use it without even thinking about it."

Although this may seem like a fantasy, ubiquitous computing will approach us in near future: during the opening plenary session of *International Electronic Device Meeting (IEDM) 2010*, Dr. Kinam Kim from Samsung declared that Samsung will develop such ubiquitous computing world before 2020.

As an essential part of merging this ubiquitous computing system with our lives, the wireless sensor network (WSN) needs to deploy many small, unnoticeable, self-sustaining sensor nodes into an environment to collect and transmit information. From now on, the term *smart dust* will be used to refer to such elementary physical devices consisting of sensors, a transceiver and supporting electronics, and which is connected to a large wireless sensor network [4].

A core challenge of such smart dust devices is to power them through out its physical lifetime (perhaps 10 years). Because the "smart dust" will be everywhere, the power supply challenge is different from existing electronic systems.

Cable wiring is the most common method of providing energy to electronic devices. But for a ubiquitous computing system, cable wiring is prohibitively expensive or even impossible in certain environments. So cable wiring is not suitable for the smart dust system.

Nowadays, batteries dominate the power supply for portable electronic devices such as mobile phones and mp3 players. There are two disadvantages: first, the energy density of the state of the art battery is still only around  $1\sim3$  kJ/cm³ [5-7], which means a cubic-centimeter battery can provide only a few hundred days of power to a *smart dust* device consuming 100  $\mu$ W; second, the self-discharge rate of the battery is  $3\sim5\%$  per month at 20 °C [5, 6], which means only 69.4  $\sim54\%$  percent energy is left after 1 year even if the battery is not connected. Recharging or replacing these batteries by humans is therefore not a good candidate for power supply to ubiquitous systems.

The development of new batteries is slow: the energy density of batteries has only increased by a factor of five over the last two centuries [7, 8]. A fundamental breakthrough will be essential for the battery to satisfy the

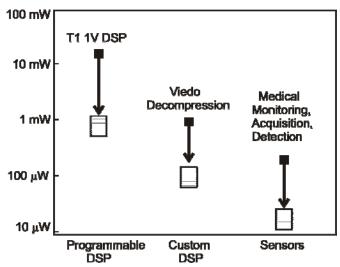

Fig. 1.2. Trends in Power consumption for low to medium throughout DSP. Modified according to [13].

demands of the fast-growing IC industry. New concepts such as the nanomaterial based battery [9], combustion-based micro-power generator [10] and micro fuel cell [11, 12], are the hopes of the future.

Advances in low-power CMOS<sup>1</sup> VLSI<sup>2</sup> have led to the dramatic decreases in power consumption. Theoretically, it was predicated that the power consumption of different motes will be below 10  $\mu$ W in the foreseeable future (shown in Fig. 1.2) [13]; practically, it was reported that a CMOS image sensor can operate continuously at 70  $\mu$ W/cm<sup>2</sup> [14] and a temperature sensor requires less than of 40  $\mu$ W continuous power supply [15].

Although global warming aggravates the demand for sustainable energy, plenty of energy sources are available at a micro-scale. As reported in [16, 17] and will be discussed in detail in Section 1.3, various energy sources, such as, solar, wind and geothermal, have energy densities in the range of tens of microwatts/cm<sup>3</sup>. All of them can provide power to the smart dust if effectively accumulated, i.e., energy harvested.

<sup>2</sup> Very Large Scale Integration

<sup>&</sup>lt;sup>1</sup> CMOS: Complementary Metal Oxide Semiconductor

## 1.2 Requirements for an Energy Harvester

The energy harvester has both intrinsic requirements as an energy source and special requirements imposed by the ubiquitous computing system. In short, the energy harvester should offer **enough** power to the smart dust **everywhere** within **limited dimensions**.

#### 1.2.1 *Power*

Intrinsically, the energy harvester should scavenge at least microwatts of power from the environment of the smart dust. This is because the power consumption of the smart dust is around  $100~\mu\text{W/cm}^2$ , and the duty cycle is generally higher than 1%. Because there is just enough energy, and because the supply and the demand may come at different times, in practice a temporary energy buffer and power management electronics are necessary to effectively deliver the energy from the harvester to the smart dust.

#### 1.2.2 Size

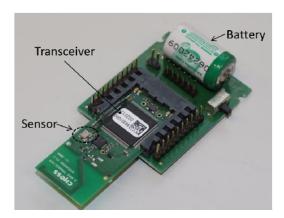

Thanks to Moore's law [18] in IC technology, the size of the smart dust is no longer the bottleneck of the system. Fig. 1.3 shows a commercially available "smart dust" including a sensor, a battery and a transceiver. The battery, which is guaranteed to have a 1-year life time, dominates both the size and the weight of the system.

Fig. 1.3. The battery dominates the size of the sensor in a commercial available sensor node. The battery's one year life time limits the life span of this sensor node.

As the alternative to the battery, the energy harvester should not be bulky. One of the key aesthetic requirements of ubiquitous computing is that it should naturally fit into our life without being noticed.

Depending on the applications, the size of the scavenger can vary, but generally we prefer a scavenger not larger than 10 cm<sup>3</sup>, which is a typical volume of smart dust [17]. Also it is ideal if the size of the energy harvester can scale with that of the smart dust.

## 1.2.3 Flexibility

The most prominent characteristic of the ubiquitous computing system is its omnipresence. So the energy harvester should also be ubiquitous. The environment of the smart dust changes according to the application, so the possible energy sources for the energy harvester also change. No simple single solution can address all applications, so the flexibility of the energy harvester will always be limited in principle. However, even the ambient of the same smart dust will have a statistical variation, and so the energy scavenger should accommodate such fluctuations. In other words, the energy harvester should have a large operating window.

The energy harvester should function typically for 10 years to be consistent with the typical physical lifetime of the electronic components in the smart dust. So the hardware of energy harvester should have excellent reliability to exploit the advantage of the infinite energy source compared to the limited energy in a battery.

## 1.2.4 Challenge of CMOS compatible manufacturing

One ubiquitous system needs hundreds of smart dust nodes, so the fabrication technology of the energy harvester should be suitable for commercial mass production. The energy harvester should be made of abundant and environmentally friendly materials. The process should be easy and have a good process control, which can offer high yield and small variability.

Most of the time, the energy harvester and the smart dust are fabricated separately, and they are assembled together and electrically connected. A more economically attractive approach is the integration of the energy

harvester and smart dust in a single chip. Such integration can miniaturize the power consumption, reduce the size and the total weight.

Normally the energy harvester can be realized before, between or after standard CMOS process for the chips. Adding the energy harvester after CMOS process flow (post-processing) will not influence the standard foundry process, thus the good-quality chip can be guaranteed. As detailed in Chapter 2 of this thesis, the different metal and insulator layers presented in the chip can be used as a part of the energy harvester, which is similar to the process discussed in [9]. Alternatively, like the renowned digital micro-mirrors [13], the energy harvester can be completely built on top of the CMOS chips which will be discussed in Chapter 4 and Chapter 5.

However the post-processing approach cannot be applied to processes or materials that require temperatures higher than 450 °C; the added extra layers of the energy harvester should not add too much excessive mechanical stress; chemical contamination, which will change the performance of the CMOS chips should be avoided; plasma charging damage is possible when the plasma enhanced chemical vapor deposition (PECVD) process is involved [19].

## 1.3 Sources for energy harvesting

There are various approaches to obtaining the "Holy Grail" for energy harvesting depending on the application. Here we discuss various energy sources from which the harvester will scavenge because this is the starting point for the design of the energy harvester.

## 1.3.1 Sunlight

Most energy used by human beings today - such as that from coal, gasoline, and oil - originate from sunlight. Sunlight is also the best choice for the energy harvester if it is available.

The average power density of outdoor sunlight is 100 mW/cm<sup>2</sup> under AM 1.5 illumination spectrum [20] and that of an indoor light may vary widely, typically from 0.1 to 1 mW/cm<sup>2</sup>, depending on e.g. the type and the position of the light source [17].

The obvious device to harvest solar energy for electric means is the photovoltaic (PV) cell, also known as solar cell. With a history of more than 50 years, there are various solar cell technologies [21]. Most have an outdoor photovoltaic (PV) efficiency more than 10% [22] and some solar cells have a good performance (more than 5%) even under weak light illumination such as indoor light [23, 24]. So if the outdoor light is available, the solar cell energy harvester can offer more than 10 mW/cm² output; for indoor light, some solar cells can still offer microwatts per square centimeter, which still meets the requirement for the energy harvester.

The reliability of solar cells is very good: off-the-shelf solar cells often come with a 20 years guarantee. The voltage output of the solar cell is almost constant under different illumination, so the operating window of the energy harvester based on light is also very large.

However, if there is no light available at all, for example, a pressure sensor system inside a car tyre, the use of PV harvester is not an option.

#### 1.3.2 Mechanical Vibrations

In nature, low-level mechanical vibrations can be found in many places, such as computer fans and microwave ovens. High-level mechanical vibrations are available from devices such as a car engine and the blades of a helicopter.

There are two important factors playing a role in a possible energy source for mechanical harvesting: the displacement and the acceleration amplitude (A) that can be induced by the source. In [16], Shad Roundy et al., showed that there are two common characteristics for all the low-level vibration sources: the displacement is greatest somewhere below 200 Hz, and the acceleration amplitude magnitude spectrum is relatively independent on frequency ( $\omega$ ). The vibration amplitude is generally in the range of 5~20  $\mu$ m [16]. Information about the vibration sources is essential to the design of vibration harvesters. As shown in [16], the energy harvester should be designed to resonate at the fundamental vibration frequency, because the maximum energy output drops rapidly with increasing mismatch between resonant frequency and stimulation frequency (see Section 2.1).

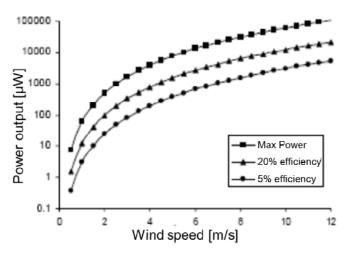

Fig. 1.4. Power density from Air flow at different wind speed and different efficiency modified according to [17].

Scavenging mechanical vibration power dominates the research community over recent years, and will be discussed in more detail in Chapter 2.

### 1.3.3 *Air flow*

Air flow is widespread, and people began to harvest wind energy more than 4000 years ago for sailing. Windmills also helped Dutch people to pump water from low-lying land into the sea. Wind power will be one of the primary green energy sources for the energy-starving world [25].

As an energy source for "smart dust", on first sight wind energy meets the requirements of the energy harvester quite well. Fig. 1.4 shows the possible energy densities versus the wind speed at three different conversion efficiencies. A power output of  $100~\mu\text{W/cm}^2$  is a realistic target even with an efficiency of just 5% at wind speed of 5 m/s.

There are reports about airflow harvesters based on the wind turbine [26-28]. Although they report promising energy output, they are relatively large devices that are incompatible with the size of the smart dust and thus unsuitable for most WSN systems. It is reported, a micro windmill of 1 cm<sup>3</sup> can generate 1 mW power at a wind speed of 40 m/s [29], and this low conversion efficiency is probably due to the relatively high viscous drag on the blades when the turbines are miniaturized [30].

#### 1.3.4 Thermal Gradient

There will be a potential difference between two dissimilar metal conductors depending on the junction temperature of these two conductors. This is the so-called Seebeck effect, and is the physical principle of a thermoelectric generator. In ambient air, there are naturally occurring temperature gradients that can provide an energy source for energy harvesting. The maximum efficiency  $\eta$  of such a thermoelectric generator is given by the Carnot's theorem [31, 32]:

$$\eta = \frac{T_{High} - T_{Low}}{T_{High}} = \frac{\Delta T}{T_{High}}$$

(1.1)

The practical efficiency is only about 10% of the theoretical maximum. For a temperature difference of 10 °C, at room temperature the maximum power output is generally less than 50  $\mu$ W/cm<sup>2</sup> [33], which is quite high compared to the alternatives.

Research has been carried out on small-scale thermoelectric energy harvesters [34-37]. Also, there are commercial thermoelectric products such as the Seiko Thermic watch.

#### 1.3.5 Human Power

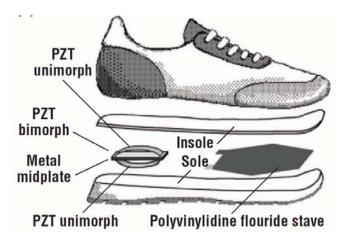

From resting to running, the human body burns 0.1~1.5 kW. An average human body burns about 10.5 MJ of energy per day, and it corresponds to an average power dissipation of 121W [38]. Human power sources are classified into passive and active sources: the active ones require humans to constantly perform in action such as shaking and cranking; the passive ones don't require humans to do anything extra to generate power. The latter is preferred for ubiquitous computing. Fig. 1.5 shows an energy harvesting shoe, which scavenging energy from human walking.

There are experimental reports of harvesting power from human walking [39-41]. The MIT group [38] showed that a piezoelectric shoe is capable of producing an average power of 330 microwatts per cubic centimeter. There are also commercially available self-winding watches powered by the kinetic energy of a swinging arm. In [42, 43], Mitcheson et al. presented a detailed

Fig. 1.5. Energy harvester that scavenges the energy from human walking [8].

analysis about the optimization of the energy harvester based on human motion.

## 1.3.6 Radiofrequency (RF) radiation

The RF spectrum is a part of the electromagnetic (EM) spectrum, and ranges from 3 kHz to 300 GHz. The energy density of the electric field of a plane EM wave is  $\mathbf{z}^{\mathbf{E}}$ , where  $\varepsilon$  is the permittivity of the medium and  $E_0$  is the electric field strength [44]. For far-field application, which is case in our application,  $E_0$  is inversely proportional to the distance from the source of the radiation.

The biggest advantage of RF radiation is its abundance. Radio, television broadcasts, mobile telephone services and wireless local area network (WLAN) cover every urban region, which makes RF radiation so pervasive that it fits the concept of ubiquitous computing well. The other advantage is that the energy harvester for RF radiation can be integrated into the microelectronic device [45], so by the standard CMOS process flow, the flexibility and the reliability are no longer a problem.

However, the disadvantage is that the power level of RF radiation is lower than that of the other sources. There is a maximum permissible human exposure (MPE) to RF radiation due to health concern. The International Commission on Nonionizing Radiation Protection (ICNIRP) [46] and IEEE

Fig. 1.6. Energy harvester based on radioisotope [54].

[47] both recommend that MPE should not exceed 1-5 mW/cm<sup>2</sup>. Due to the typical long distance from the RF source, RF Power is normally orders of magnitude smaller than 1 mW/cm<sup>2</sup> in most places; generally less than  $10 \,\mu\text{W/cm}^2$  [48, 49].

If the RF radiation source is close to the smart dust, RF radiation harvesting is successful with the involvement of the human activity such as pushing the button of sending signal [45, 50, 51]. For the RF radiation energy harvester the design of the antenna is important [52], and the size of the antenna prefers to be larger than the wavelength of the RF radiation [53].

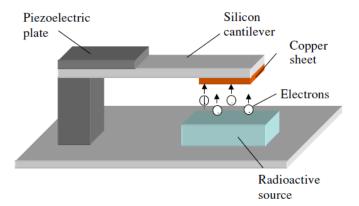

## 1.3.7 Radioisotope

When a radioisotope atom decays into a more stable one, it releases certain particles that have certain amount of energy. It is possible to harness the energy released by this decay process, but with a relatively low conversion efficiency [55, 56].

Fig. 1.6 shows the principle: the electron released from the radioactive source electrostatically charge the copper sheet, thus the electrostatic field will increase. The beam will be attracted downwards, until it touches the source. Upon touchdown the electrons in the copper sheet will be neutralized by the conductive radioactive source, thus the beam is released to vibrate at its resonant frequency, allowing energy harvesting from the piezoelectric plate.

| Harvester           | Reference                   | area (mm2) | power/area<br>(μW/mm2) | Requirements                  |  |

|---------------------|-----------------------------|------------|------------------------|-------------------------------|--|

| solar cell, outdoor | Green [22]*                 | \          | 50-200                 | AM1.5 (sunlight)              |  |

| solar cell, indoor  | Van Veen [59]<br>Reich [24] | \          | 0.01~1                 | Indoor lighting,<br>1-10 W/m2 |  |

| Piezoelectric       | Elfrink[60]                 | 49         | 0.49                   | Good frequency match required |  |

| Electromagnetic     | Jones [61]                  | 99         | 0.37                   |                               |  |

| Electrostatic       | Arakawa [62]                | 400        | 0.015                  |                               |  |

| Thermo-electric     | Böttner [37]                | 1.12       | 0.6                    | Gradient > 5 °C               |  |

| Micro-windmill      | Holmes [29]                 | 113        | 0.02                   | 5 m/s wind speed              |  |

Table 1.1. Comparison between (presumably CMOS-compatible) energy harvesters.

One advantage of a radioisotope energy generator is that radioactive materials can provide extremely high energy densities and over extremely long life time. However, the key disadvantage is that the use of radioactive material can be a serious health hazard and is therefore highly controversial.

## 1.4 Advantage of a solar cell as an energy harvester

From aforementioned sections, we know that energy harvesting is promising for smart dusts of ubiquitous computing systems, and there are many approaches based on different energy sources.

A comparison of energy harvesting techniques is presented in Table 1.1. The table is limited to approaches which are likely CMOS-compatible. This compatibility allows a high level of integration, a prerequisite for low cost mass fabrication. For the energy harvesters using mechanical vibration, only those matching general vibration sources [57] are included. The performance comparison is made per surface area (as in [58]), because CMOS power consumption scales with chip area. The table makes clear that solar cells can provide competitive power levels, even indoor. In addition, ac to dc conversion is required for most alternatives, but not for photovoltaics (PV).

On the size scale of microchips, thin-film solar cells can be considered to have the most mature of the technologies among those listed in Table 1.1. They offer both long-term reliability (> 20 years) and low-cost mass-production. From the system perspective, their merits include the delivery of

<sup>\*:</sup> There are more than 10 types of solar cells, and they have different efficiencies. Here only a range is given.

(

dc power and an output voltage hardly dependent on the illumination intensity. Last but not least, the photovoltaic (PV) power generation will scale with chip area, just like a chip's power consumption. So solar cell as an energy harvester is a good choice for a smart dust, but on-CMOS chip solar cells as energy harvesters have not been explored yet.

#### 1.5 Outline of the thesis

In this thesis, two types of energy harvesters on top of the CMOS chips are presented.

Chapter 2 discusses the energy harvester based on mechanical vibrations. After a general mathematical model for the vibration based energy harvester, three main-stream types of vibration-based energy harvester will be described. Then a schematical design of our energy harvester will be given, and results of the modeling of this device are also given. Finally, the challenges of the vibration-based generator are presented.

Chapters 3~5 are devoted to using two types of solar cells as for energy harvesting: the amorphous silicon solar cells (a-Si) and the copper indium gallium (di)selenide (CIGS) solar cells. Chapter 3 describes the motivation of the monolithic solar cell integration on top of a CMOS chip, the selection of the solar cell technology and the types of CMOS chips that used. Then the influence of the passivation layer on CMOS performance will be given. Chapter 4 deals with integration of the amorphous silicon (a-Si) solar cells, and chapter 5 deals with the integration of the CIGS solar cells.

Final conclusions and future recommendations are given in Chapter 6.

## Chapter 2. Vibration based energy harvester

As described in Section 1.3.2, mechanical vibrations were quickly acknowledged as the most ubiquitous energy source, thus it has received intensive research attention in the past. In this chapter, more details about the vibration-based energy harvester will be given along with a modeling study of an integrated electromagnetic based generator.

## 2.1 General model for vibration conversion

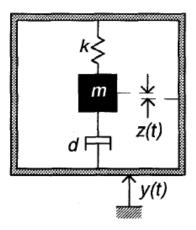

A vibration based power generator for an energy harvester is typically based on a mass-spring structure enclosed in a frame as shown in Fig. 2.1. Acceleration applied to the frame is coupled to the mass only by the spring, and results in a change to, generally an increase in, the spring's potential mechanical energy. A mechanical-to-electrical converter then transforms the stored mechanical energy into electrical energy.

A simple but practical model based on Fig. 2.1 was proposed by William and Yates in [63]. They used Eq. (2.1) to describe the kinematic behavior of the energy harvester, and based on that they obtained the generated power as described by Eq. (2.2).

$$m\vec{z} + c\vec{z} + kz = -m\vec{y} \tag{2.1}$$

where z is the spring deflection, y is the frame displacement, m is the proof mass, c is the damping coefficient, k is the spring constant.

Fig. 2.1. Schematic diagram of the vibration based generator [63].

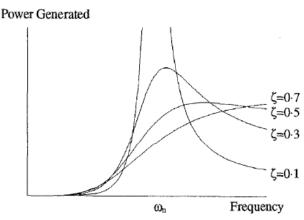

Fig. 2.2. Frequency spectrum of power generation around the resonant frequency of the mass-spring system for different damping factors [63].

$$P = \frac{m\zeta Y_0^2 \left(\frac{\omega}{\omega_n}\right) \omega^3}{\left[1 - \left(\frac{\omega}{\omega_n}\right)^2\right]^2 + \left[2\zeta \frac{\omega}{\omega_n}\right]^2}$$

(2.2)

where P is the power output,  $\zeta$  is the damping ratio,  $\omega$  is the frequency of energy sources,  $\omega_n$  is the resonant angular frequency of the energy harvester,  $\mathbb{F}_0$  is the amplitude of the vibration source.

If the resonant frequency of the mass-spring system matches the frequency of the energy source, i.e.,  $\omega = \omega_n$ , Eq. (2.2) can be reduced to Eq. (2.3) and Eq. (2.4).

$$P = \frac{mY_0^2\omega^2}{4\xi^2} \tag{2.3}$$

$$P = \frac{m\zeta(\omega^2 Y_0)^2}{4\zeta^2 \omega} = \frac{mA_0^2}{4\zeta \omega}$$

(2.4)

where  $A_0 = \omega^2 Y_0$  is the acceleration amplitude.

From Eq. (2.2), we can plot the possible power output from energy harvesters with different damping ratio versus the resonant frequency of the vibration source (Fig. 2.2).

From the Eq. (2.2) and Fig. 2.2, we can make the following design rules for the energy harvester for maximum power generation:

a) The proof mass should be as heavy as possible within the size allowed.

- b) The resonant frequency of the energy harvester should match the frequency of the energy source as much as possible.

- c) The mechanical damping should be small.

From Eq. (2.3) and Eq. (2.4), we can make the following selection rules for vibrational energy sources, if there are multiple vibration sources available:

- a) If the frequencies of the vibration sources,  $\omega$ , are similar, find a place where the vibration amplitude  $Y_0$  is the maximum.

- b) If the acceleration amplitudes,  $A_0$ , are on the same level, the vibration that has a lower frequency,  $\omega$ , is preferred.

## 2.2 Types of vibration based energy harvester

At the beginning of the energy harvesting era [57, 63], three types of vibration-based energy harvesters were developed worldwide, categorized by the conversion mechanism from kinetic energy to electricity. These will be discussed in the following subsections.

## 2.2.1 Electromagnetic energy harvester (EM harvester)

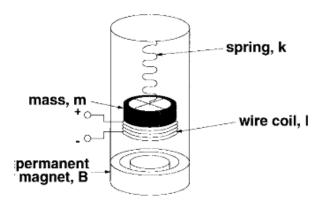

An electromagnetic generator is a micro-scale dynamo, which utilizes Faraday's law, i.e., a voltage is "induced" in a coil when the coil moves relatively to a magnetic field. The relative movements are caused by the mechanical vibrations (See Fig. 2.3).

The biggest advantage of the electromagnetic generator is that: if the energy harvesters have the same size, it can, theoretically, provide the largest possible power output [17]. The practical realization is rather simple [13, 61, 63]. When miniaturized, the resonant frequency of the EM harvester can match the frequency (below 200 Hz [16]) of the low level vibration sources [61, 64-66].

A disadvantage is that with the scaling down of the size, the output voltage of electromagnetic generators are alternative and small, generally smaller than 0.2 V, so a transformer will be needed. Another disadvantage is that the monolithic integration of a permanent magnet is difficult [67, 68].

Fig. 2.4: Schematic diagram of an EM energy harvester [13]. The cylinder shell should be attached to the vibration energy source.

Fig. 2.4. Schematic diagram of an electrostatic energy harvester [43, 69]. The anchor and the stationary electrode are to be fixed with respect to the vibration energy source.

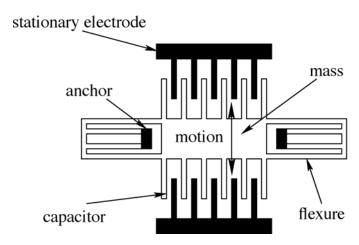

## 2.2.2 Electrostatic energy harvester

Fig. 2.4 shows the schematic diagram of an electrostatic energy harvester. Before operation, the capacitor (C) between the mass and the stationary

electrode has a charge Q, so the energy stored is  $\overline{2}$ . When the vibration of the energy sources causes movement of the mass, the capacitance (C) between the mass and the stationary electrode varies, leading to a change in voltage. Thus, the mechanical energy can be converted into electrical energy.

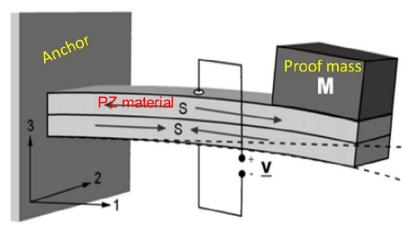

Fig. 2.5: Schematic diagram of a piezoelectric energy harvester [73]. The beam is coated with piezoelectric (PZ) material on both sides; the anchor will be attached to the vibrational source.

The advantage of the electrostatic energy harvester is the easy integration into electronic devices by MEMS<sup>1</sup> process technologies using a process similar to integrated accelerometer manufacturing [43, 70]. The down scaling of the energy harvester, thus obtaining a smaller size, is easier than for the other types of vibration energy harvesters. What's more, the electrostatic energy harvester can be operated at non-resonant mode [71].

The disadvantage of the electrostatic energy harvester is that it needs an external voltage source to give the initial charge Q to the capacitor. It was proposed to solve this by using an electret as a long-lasting charge source [72].

## 2.2.3 Piezoelectric energy harvester

Fig. 2.5 shows a schematic diagram of a piezoelectric (PZ) energy harvester. A piezoelectric generator is based on the physical phenomenon that, when a piezoelectric material deforms due to motion-induced stress or strain, the polarizations of the electric dipoles are changed. This leads to a voltage difference, thus kinetic energy is converted into electric energy.

The advantage of the PZ energy harvester is that it has high energy density and can be integrated with electronic devices by MEMS technology. The

<sup>&</sup>lt;sup>1</sup> Micro-electro-mechanical-system

voltage of the output energy harvester can be more than 10 volts, so upconversion is not necessary [17, 74].

The disadvantage is that the resonant frequency of the PZ energy harvester is higher than that of the ambient vibration sources normally available when the energy harvester is miniaturized. The latter has a typical value below 200 Hz, and the former is well above 1 kHz [54, 74, 75]. Also the PZ material is brittle, so long term mechanic wear out may limit the lifetime of the energy harvester [74].

## 2.3 Modeling of an integrated EM harvester

All the three aforementioned energy conversion mechanisms have the pros and cons. Taking the requirements of the energy harvester into account (Section 1.2), an on-chip integrated EM harvester by CMOS compatible post processing technology is modelled to study the feasibility of its practical implementation.

In this section, we presented the design of the EM energy harvester and the preliminary simulation results.

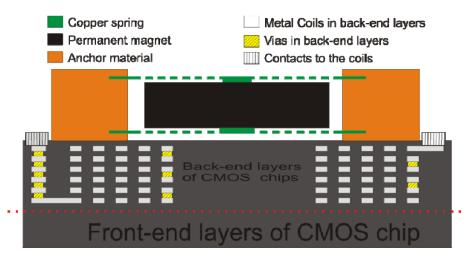

## 2.3.1 Design of the new EM energy harvester

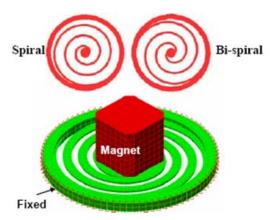

Fig. 2.6 depicts the design of our EM harvester: coils, springs, and a permanent magnet.

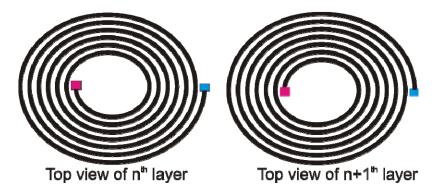

The coils are embedded in the CMOS chip, i.e., the coils will be made by metal layers during back-end-of-line processing. So the coils can have 6-8 layers, depending on the choice of (deep-submicrometer) CMOS technology. The standard vias are used to connect the successive layers. As shown in Fig. 2.7, the via-connections and the design of the coil layer are done in such a way that all the coil layers are connected in series.

The mass-spring and the permanent magnet of the EM harvester will be post-processed. Fig. 2.8 shows the design of the spiral or bi-spiral shaped spring, and such designs can provide a low resonant vibration frequency compared to the cantilever beam based spring of an EM generator [64].

The permanent magnet will be attached to the center of the spring, and will act as the mass at the same time. If we choose cobalt platinum (Co-Pt) based

Fig. 2.7. Schematic diagram of the micro scale EM generator (not to scale)

Fig. 2.7. Design (top view of) of the successive coil layers. The spirals are directed clockwise and anti-clockwise, alternatively. Such design makes sure that the EMFs of different layers are superimposed, not canceled.

permanent magnetic material for purpose of monolithic integration [76, 77], then the height of the permanent magnet could not exceed 100 µm.

#### 2.3.2 Numerical Simulations

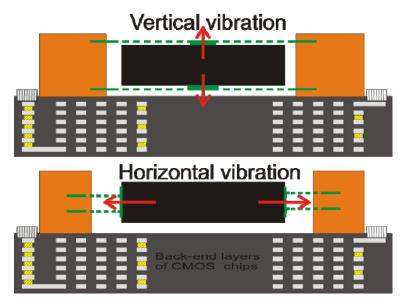

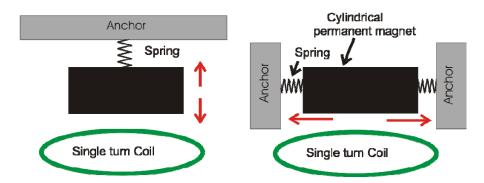

There are two possible vibration directions of the permanent magnet with respect to the embedded coil: vertical and horizontal, as shown in Fig. 2.9.

Fig. 2.9. The design of the spring aims for low frequency vibration (adopted from [64]).

Fig. 2.9. The permanent magnet have two possible vibration directions with respect to the coil layers. The positions and the directions of the coil layers are fixed by CMOS technology.

Numerical simulations have been carried out, by using a COMSOL FEMLAB code [78], to find the amount of power output.

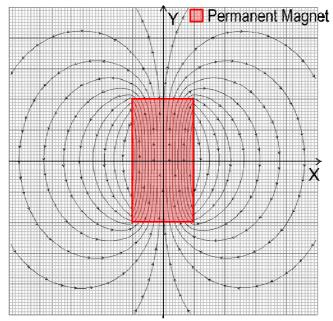

## 2.3.2.1 Theory of Magnetic field from a Permanent Magnet

From Farady's law, the voltage across the coil ends is proportional to the change of the magnetic flux through the coil. The magnetic flux is induced by

Fig. 2.10. Stray field of a cylindrical permanent magnet simulated by Visimag [79].

the permanent magnet, so the starting point of the COMSOL simulation is the calculation of the magnetic field distribution of a permanent magnet.

Qualitatively, Fig. 2.10 shows a two dimensional magnetic field of a cylindrical permanent magnet.

For infinite element analysis, the permanent magnet is composed of many small pieces, and each of them is called an element. Each element inside the permanent magnet will have its own residual magnetization M, volume size  $d\mathbf{v}'$  and surface area  $d\mathbf{s}'$ . Each small element will give its own contribution to the magnetic field strength according to Eq. (2.5) - Eq. (2.7). The magnetic field strength at certain position  $\mathbf{x}'$  is a superposition of all the small permanent magnet elements.

$$\overline{\mathbf{B}_{(\vec{k})}} = \nabla \times \overline{\mathbf{A}_{(\vec{k})}}^{\dagger}$$

$$= \frac{\mu_0}{4\pi} \iiint_{M(\vec{k}')} \times \frac{\vec{x} - \vec{x}^{\ell}}{\left|\vec{x} - \vec{x}^{\ell}\right|^3} dv^{\ell} + \frac{\mu_0}{4\pi} \oiint_{M(\vec{k}^{\ell})} \times \frac{\vec{x} - \vec{x}^{\ell}}{\left|\vec{x} - \vec{x}^{\ell}\right|^3} ds^{\ell} \tag{2.5}$$

where,  $\overrightarrow{x'}$  is the coordinate of the contributing permanent magnet element,  $\overrightarrow{x}$  is the coordinate where we are interested in,  $d\mathbf{v'}$  is the volume of the contributing permanent magnet element,  $d\mathbf{s'}$  is the surface area of the contributing permanent magnet element,  $\overrightarrow{B}$  is the magnetic field strength,  $\overrightarrow{A}$  is the magnetic vector potential, I is the vacuum permeability,  $\overrightarrow{I}$  is the magnetic volume current density,  $\overrightarrow{I}$  is the magnetic surface current density.

The magnetic current density  $\overline{J_M}$  and  $\overline{J_M}$  are given by Eq. (2.6) and Eq. (2.7) respectively:

$$\overline{J_{M(n')}} \equiv \nabla \times \overline{M_{(n')}} \tag{2.6}$$

$$\overline{\mathbf{I}_{M(\mathbf{s}')}} \equiv \overline{M_{(\mathbf{s}')}} \times \overline{\mathbf{n}} \tag{2.7}$$

where  $\vec{n}$  is the surface normal vector to the surface ds at position  $\vec{x}^{l}$ .

These equations can be derived from the Maxwell equations under the quasi static assumptions [80], which are applicable to our case due to the small size of the EM generator and the low vibration frequency.

#### 2.3.2.2 Model

For finite element analysis, a smaller size element will lead to more accurate results. However, the number of the elements is practically limited by computer memory size and computation speed.

An AC/DC module of COMSOL 3.3a has been used to perform the numerical simulations. The mesh of the simulated structure consisted of 39000 elements, i.e., square blocks; the number of degrees of freedom to be solved was 640000. The COMSOL simulates the magnetic field according to Eq. (2.5) - Eq. (2.7), listed in Section 2.3.2.1.

Due to time limitations, simulations are done based on the layout depicted in Fig. 2.11, which is a simplified version of Fig. 2.9. The following text specifies the input parameters for the simulation:

- a) The cylindrical permanent magnet has a height of 50  $\mu m$ , a radius of 50  $\mu m$ .

- b) The permanent magnet has a residual magnetization of 0.5 tesla, and its magnetization direction is along the axis of the coil.

Fig. 2.11. Schematic diagram of the EM-generator model simulated by COMSOL.

- c) The resonant vibration frequency of the EM harvester is set to 100 Hz.

- d) The vibration amplitude of the EM harvester is set to 5  $\mu$ m, the space between the coil and the permanent magnet is 10  $\mu$ m.

- e) For this simulation, only a single turn coil with a radius of 60 μm is used. For multiple-turn coils, similar simulations can be carried out.

Input parameters a) and b) for the permanent magnet are based on properties of the CMOS post-processed Co-Pt material [76, 77]. The neodymium-iron-boron (Nd-Fe-B) based permanent magnets offer a higher residual magnetization (1 tesla) [81], but only for a higher process temperature (500 °C) [82], not allowing CMOS post-processing.

Inputs parameters c) and d) are related to the vibration of the EM harvester, which corresponds to an acceleration amplitude of 0.2g (g is the standard acceleration due to free fall). These parameters are based on the properties of the generally available low-level vibrations (see Section 1.3.2). Here we select a typical value of 100 Hz, which can be achieved by tuning the thickness of the spring and the weight of the permanent magnet.

#### 2.3.2.3 Simulations Results

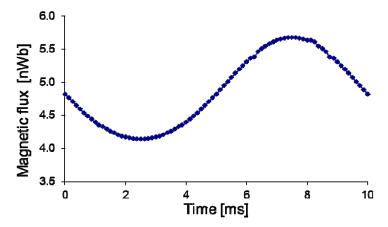

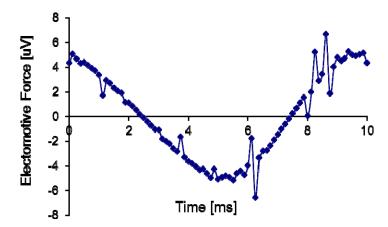

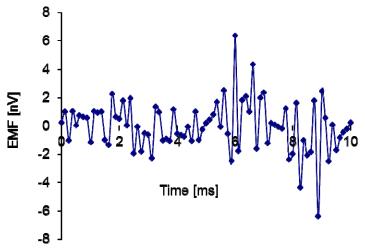

For the vertical-vibration simulations, as shown on the left in Fig. 2.11, the magnetic flux through the coil and electromotive force (EMF), i.e., the voltage output of the coils, inside the coil versus time are shown in Fig. 2.12 and Fig. 2.13, respectively.

Fig. 2.13. Magnetic flux through a single-turn coil at 100 Hz for vertical vibrations. The simulation results are shown for one period of time, i.e., 10 ms.

Fig. 2.13. EMF of a single turn coil at 100 Hz (vertical vibrations). The simulation results are shown for one period of time, i.e., 10 ms.

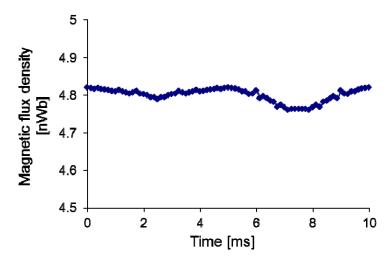

For horizontal vibration as shown on the right side in Fig. 2.11, the magnetic flux through the coil and EMF of the coil versus time are shown in Fig. 2.14 and Fig. 2.15, respectively.

The trend of the horizontal vibrations is not as clear as that of the vertical vibrations. This is due to the large element size in the simulation. More precision could be obtained by a finer computation mesh, however from the results it is clearly established that horizontal movement generates negligible power, so no further study of this mode was pursued.

Fig. 2.15. Magnetic flux through a single-turn coil at 100 Hz for horizontal vibrations. The simulation results are shown for one period of time, i.e., 10 ms.

Fig. 2.15. Electromotive force of a single turn coil at 100 Hz for horizontal vibrations. The simulation results are shown for one period of time, i.e., 10 ms.

## 2.3.2.4 Power estimation and possible improvements

Assuming a  $1 \times 4 \,\mu\text{m}^2$  cross section of the coil with the same conductivity as Cu ( $6 \times 10^{5}$  siemens/m [96]), which is the same material of the metal layers in CMOS chips, the coil resistance  $R_{\bullet}$  is given by:

$$R_0 = \frac{L}{\sigma S} = \frac{60 \times 2\pi \times 10^{-6}}{6 \times 10^7 \times 4 \times 10^{-12}} = 1.6 \Omega$$

(2.8)

From Fig. 2.13, the maximum EMF of the vertical vibrations, which is induced voltage (V) inside the coil, is about 5  $\mu$ V, so one can obtain the maximum power, that can be extracted, is half of the power dissipated:

$$P_1(\max_1 vertical) = V^{\dagger} 2/(2R_1 0) = 7.8 \text{ pW}$$

(2.9)

From Fig. 2.15, it is difficult to extract the maximum EMF of the horizontal vibrations because its excursions are difficult to distinguish from noise. The averaged EMF should be orders less than that of the vertical vibrations.

Based on this modeling estimate, we can conclude that a picowatt power output can be obtained from one single-turn coil and the small Co-Pt based magnet. As specified in Section 1.2, we need to increase the power output to the microwatt range. Because the PM magnet's size is limited due to the fabrication technology [76, 77], and because of the size limitations for smart dust, we consider two other possible ways to improve the power output.

First, for each small EM harvester, we increase the number of coil turns to  $N_1$ , the improvement of the power output is proportional to the number of coil turns:

$$P = \frac{V^2}{2R} = \frac{1}{2N_1 R_0} \left(\frac{N_1 d\phi}{dt}\right)^2 = N_1 P_0$$

(2.10)

where we assume,  $R_{\bullet}$  is the resistance of one single-turn coil,  $R_{\bullet}$  is the power extracted from the single-turn coil.

Second, like batteries connected in series, we can connect a lot of small EM harvesters in series. The improvement of the power output is proportional to the number of the EM harvesters connected (if the EM harvesters vibrate in phase).

If we use  $N_2$  to denote the number of EM harvesters connected, then the power output will be given by Eq. (2.11).

$$P = N_a N_a P_a \tag{2.11}$$

As to the value of  $N_1$ , it can have a decent value of  $20\sim30$ . Because in our design the coils of the EM harvester are a part of the metal layers of the CMOS chip, the number of coils layers should be the same as that of the metal layers. In each layer, the number of coils is limited by the size of the small permanent magnet. Assume a typical 6-metal layers CMOS chip, and each layer having  $4\sim5$  turns of the coil, the value of  $20\sim30$  for  $N_1$  is realistic.

As to the value of  $N_2$ , it is limited by the total size of the smart dust. For a typical smart dust size of 1 cm<sup>3</sup>, the number of the allowed small EM harvesters is given by Eq. (2.12).

$$N_2 = \frac{1 \text{ cm} \times 1 \text{ cm}}{128 \text{ } \mu\text{m} \times 128 \text{ } \mu\text{m}} = 6400 \tag{2.12}$$

Note: assuming the space between the adjacent small EM harvester to be 5  $\mu m$ , the diameter of the small permanent magnet is 120  $\mu m$  and the total size of the magnet matrix size of 1 cm<sup>2</sup>.

So according to Eq. (2.11), the total possible power can be:

$$P = N_1 N_2 P_0 = 30 \times 6400 \times 7.8 \, \text{pW} \approx 1.5 \, \mu\text{W} \tag{2.13}$$

So the numerical simulation shows that the vertical vibrations of the permanent magnet offer higher power output, and energy scavenging in the microwatt range is possible by connecting a matrix of small energy harvesters in series.

#### 2.3.3 Discussion

Ching, *et al.* reported a power output of 830  $\mu$ W [64], which is the highest power output of a micromechanical EM harvester according to my knowledge. Compared to that, the power output from our model is very low.

There are two reasons: the permanent magnet used by Ching *et al.* is Nd-Fe based off-the-shell product which has a higher magnetic field; and the vibration amplitude of their EM harvester is set to 200  $\mu$ m, which is 40 times larger than that used in our simulations.

According to Eq. (2.2) - Eq. (2.4), the power output is proportional to the square of the vibration amplitude. If we take this into account, then our simulation result is comparable to Ching's experimental value.

## 2.4 Frequency match challenge

As shown in Section 2.1, the vibration based energy harvester harnesses the harmonic oscillation that the vibrating energy source stimulates. In turn, ensuring proper oscillatory motion plays a major role in the resonant converter design.

Due to the omnipresence of the vibration energy source, the vibration-based energy harvester attracts attention of the researches for already many years. Within the last several years, researchers of vibration-based power generation acknowledged a huge challenge: the frequency match.

First, the resonant frequency of the vibration-based energy scavenger is often larger than 1 kHz [43, 75] when one tries to miniaturize the scavenger down to cubic centimeter size. Most of the available ambient vibration energy sources have a frequency below 200 Hz [16]. So these two frequencies are difficult to match. As can be seen from Eq. (2.2), the output power will decrease exponentially with increasing of this mismatch.

Second, the bandwidth of the resonance peak of the miniaturized energy harvester is less than 5 Hz [43, 75, 83]. The smart dust concept does not allow for large arrays of harvesters with their own resonant frequency. So such a narrow bandwidth will limit the flexibility of such energy harvester, i.e., for every application and for every ambient vibration source, a specific energy harvester has to be designed for obtaining a good match.

Although there are efforts in addressing the frequency match problem (unfortunately still leading to a reducing power output) [84-88], there is no practical way to overcome this fundamental challenge.

#### 2.5 Conclusions

In this chapter, the vibration-based energy harvester has been discussed. An EM energy harvester suitable for monolithic above-CMOS-chip integration is proposed. The numerical simulation results show that, within the most practical device dimensions (1 cm<sup>3</sup>), the power output in the micro-watt range is feasible and the results are comparable to those found in literature.

However, the practical realization of the proposed design has not been pursued due to the following reasons:

- 1. The MESA+ Nanolab offers no multilevel metallization capabilities, nor thick-film magnetic layer depositions. Experimental work would therefore depend on the cooperation with two external parties: one for the metallization, another for the magnet.

- 2. The frequency-match problem mentioned in Section 2.4 convinced us that, even if finally our EM harvester was successful, the operating

window would be very small. Thus the application would be seriously limited and not suitable for mass production.

Considering the aforementioned practical difficulties and under the shadow of the fundamental limitation of the vibration-based harvester, we decided to focus on thin-film solar cell approaches for energy harvesting as described in the following chapters of this thesis.

# Chapter 3. Solar cells on top of CMOS chips as energy harvester

In this chapter, the idea of monolithic integration of a solar cell on top of deep-submicron CMOS microchips as an energy harvester for "smart dust" is presented. First, a brief introduction to solar cells will be given, followed by the selection of solar cell technology for the integration. Further the results of the deposition of passivation layers, essential for protecting the CMOS chip, will be presented.

# 3.1 Choice of the technology

As already discussed in Section 1.4, solar cell is a competitive candidate as an energy harvester. In this section, we detailed the reasons for monolithical integration thin-film amorphous-silicon (a-Si) solar cells and copper indium gallium (di)selenide (CIGS) solar cells on top of CMOS chips without changing either the CMOS process or the conventional solar cell process flow.

# 3.1.1 Monolithic Integration

There are two approaches to realize a solar-cell-based energy harvester: hybrid-assembled and monolithic integration. Hybrid assembly is off-the-shelf, allows rapid prototyping, and offers the freedom of using different sizes for the energy generating and the energy consuming parts.

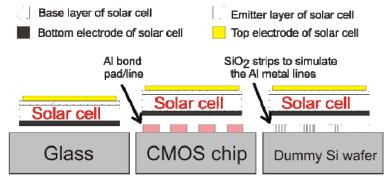

On the other hand, monolithically integrated devices bear the promise of a smaller overall size, and reduced manufacturing cost per system. Because the processes such as flip-chip/ball grid arrays, yields are sometimes much lower than 100%, in particular for off-mainstream products, so the monolithic integration may also offer a higher yield. The existing silicon on bulk-silicon [89] or on SOI [90] wafer can be used as the photo conversion medium. Our approach takes a different route, along the "Above-IC" processing philosophy (see e.g. [19]). By creating a photovoltaic cell above an existing IC, the transistor and interconnect density are uncompromised and freedom of choice appears for the solar cell technology. We will discuss the particular choice of the solar cell technology in the next section 3.1.2.

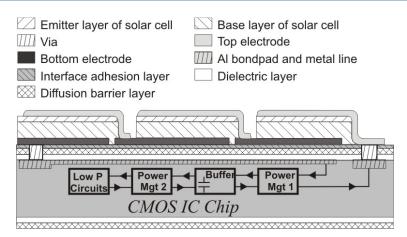

Fig. 3.1. Envisaged autonomous microchip comprising of a PV cell for energy collection, power management circuits, integrated energy storage (e.g. high-density capacitor or solid-state battery) and low-power circuits. The PV cell can be realized on the chip's front or back side.

The conversion efficiency is higher than that of hybrid assembly due to the minimized wiring. Less area is lost for daisy-chain connections, as standard lithography can be used on wafer scale production, contrary to large scale photovoltaic (PV) production [91]. Finally, smaller cell sizes typically lead to a 3~5% [22] efficiency boost.

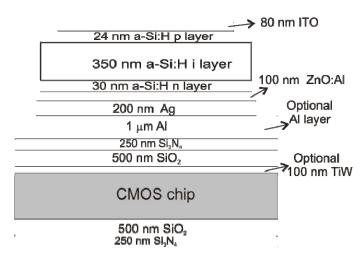

Fig. 3.1 shows the monolithic integration of a solar cell on a chip by "above-IC" CMOS post-processing. The daisy-chained solar cells convert light into electricity; the generated power is supplied to the underneath CMOS chips by the vias and the aluminum leads. The chip electronics, besides the low power functional circuits, include energy storage and management modules (common to all energy-harvesting systems). Temporary energy storage can be provided using an integrated high-density capacitor or solid-state battery. One possible attractive approach (not pursued in this work) is to employ the upper interconnect layers of the CMOS chip to this purpose. Between the CMOS chips and the solar cells, an intermediate film (or stack of films) is required to serve three purposes: for electrical insulation, to create a diffusion barrier against impurity contamination and for a better adhesion.

# 3.1.2 Solar cells selected as energy harvesters

In this section, we show that a thin-film amorphous-silicon solar cell and copper indium gallium (di)selenide (CIGS) solar cells are good candidates to be manufactured directly on a CMOS chip.

# 3.1.2.1 Brief history

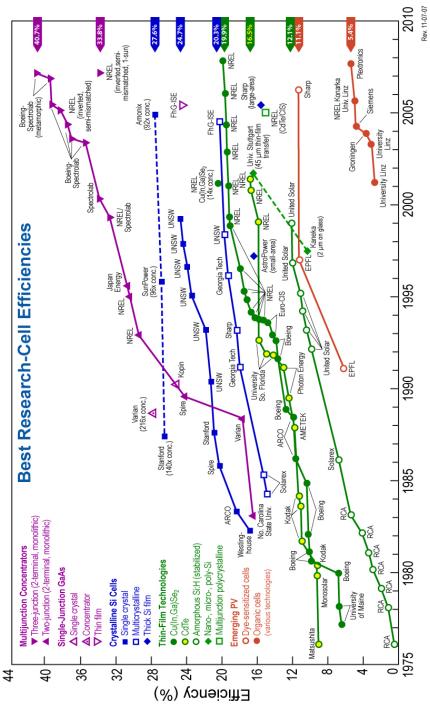

Solar cells or photovoltaic (PV) cells generate electricity when illuminated by sunlight or artificial light. The discovery of the photovoltaic effect is normally ascribed to Becquerel in 1839 [92], and selenium based solar cell, the first direct conversion of the energy of light into electricity energy, was invented by German physicist, Fritts, in 1883 [92]. In 1954, Chapin *et al.*, from Bell laboratories, fabricated the first modern silicon solar cell with 6% efficiency [93]. Due to the persistent research efforts worldwide, mainly in USA, Europe and Japan, more than 10 solar cell technologies emerge and the highest efficiency reaches to 27.6% and 32.0% for single-junction and multijunction solar cells, respectively [22]. Fig. 3.2 shows the solar cell efficiency evolvement in the last century for different technologies [94]. Due to the awareness of the global warming, carbon-free energy becomes more and more impotant in the past 10 years. As the world's major renewable green energy source, the solar cell has huge development in the past 10~20 years.

However, it is more or less generally accepted that among all the solar cell technologies, only those using thin films are likely to be able to reach the very low costs and can meet the long term demands of the electricity and energy market [95]. Nowadays, there are three main thin film technologies that are successfully commercialized: a-Si, CdTe and CIGS solar cells. In 2011, the record efficiencies are 10.1%, 16.7%, 20.3% for a-Si, CdTe and CIGS solar cells, respectively. Fig. 3.2 also shows the evolvement of these three types of thin film solar cells end by the of last century [94].

Fig. 3.2. Solar cell efficiency evolvement of different technologies [94].

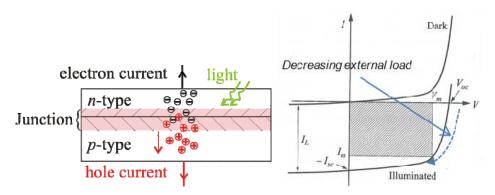

Fig. 3.3. Simplified physical model of a solar cell. Left, solar cell as a p-n diode to convert light to electricity; right, typical p-n diode I-V characteristics of a solar cell with decreasing external load under dark and illumination.

#### 3.1.2.2 Basic theory

Intrinsically, most of the solar cells can be viewed as a p-n junction diode. The basic principle of the solar cells is fully explored in many books [21, 96-99], and here only a concise and qualitative description is given.

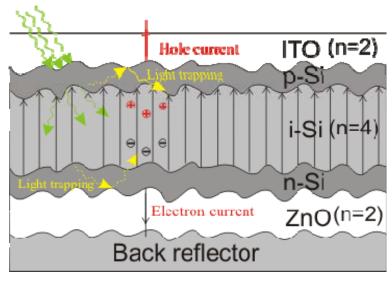

Fig. 3.3 shows the simplified physical model of a solar cell and the I-V characteristics of the solar cell in dark and under illumination with light. On the left-hand side, the electron and hole pairs (EHPs) are generated after the photon is absorbed by the solar cell material, which is a semiconductor p-n junction for most of the PV technologies. Before electron and hole recombine, the internal electric field at the p-n junction of the solar cell has to separate them, driving the electrons to the n-region and holes to the p-region.

In the absence of external connections, the drift current is exactly offset by a reverse diffusion current caused by the carrier concentration gradient. This leads to the open-circuit voltage ( $V_{ax}$ ), being established across the contacts to the two regions. At this point, no current flows through the load.

With an external load across the external contacts to the device, the photo generated excess carriers will flow through the load, thus giving a PV current. When the device is fully short-circuited, the short circuit current ( $I_{sc}$ ) flows though the load, and no net voltage appears across it.

Fig. 3.4. Simplified electrical circuit model of a solar cell under illumination [96].

The maximum power,  $\Gamma_{\text{max}}\square$ , generated by the device, is defined by the following equation:

$$P_{\text{max}} = (VI)_{\text{max}} = V_{\text{m}}I_{\text{m}} \tag{3.1}$$

Solar cells should operate at the maximum power point, where the system can operate most efficiently. This is indicated as the shadowed region indicated on the right in Fig. 3.3.

The fill factor (*FF*) measures the sharpness of the I-V curve and is defined:

$$FF = \frac{V_{\text{in}}I_{\text{in}}}{V_{\text{od}}I_{\text{eq}}} \tag{3.2}$$

And the solar cell efficiency  $(\eta)$  is the ratio of the maximum power output to the incident power of the illuminating light,  $P_{solar}$ :

$$\eta = \frac{V_{\rm m}I_{\rm m}}{P_{\rm solar}} \tag{3.3}$$

Fig. 3.4 shows a simplified equivalent electric circuit of a solar cell under illumination. From this model, the total current under illumination is a sum of the dark current and the photo generated current:

$$I = I_s \left( \sigma^{qV} f_{kT} - 1 \right) - I_L \tag{3.4}$$

where  $I_{\mathfrak{F}}$  is the saturation current, and its value can be obtained be from Eq. (3.5), V is the bias voltage of the solar cell, q is the unit electric charge, k is the Boltzmann constant, T is the operating temperature of the solar cell,  $I_{\mathfrak{F}}$  is the photo generated current, and roughly equals to short circuit current,  $I_{\mathfrak{F}\mathfrak{C}}$ .

$$I_s = I_{so} \left( e^{qV_{oc}} / k_T - 1 \right)^{-1} \approx I_{so} e^{-qV_{oc}} / k_T$$

(3.5)

In practical, Eq. (3.6) predicts *I-V* characteristics of a solar cell [100].

$$I = I_s \left( e^{Q(t-tK_s)} I_{nkT} - 1 \right) - I_L \tag{3.6}$$

1

Table 3.1: Solar cell efficiency at outdoor (AM 1.5) and indoor light illumination conditions. Data are from [23, 24, 105]. The indoor light is the reduced-intensity AM1.5 spectrum; the c-Si, a-Si solar cells are the commercial products, the others are laboratory samples (see references [23, 24, 105]).

|                                 | Bulk solar cells |       | Thin-film solar cells |      |      |       |  |

|---------------------------------|------------------|-------|-----------------------|------|------|-------|--|

| Light intensity                 | c-Si             | GaAs  | Photo-<br>chemical    | CdTe | a-Si | CIGS  |  |

| Outdoor<br>AM1.5                | 12.5%            | 12.4% | 4.0%                  | 4.7% | 7.5% | 12.9% |  |

| Indoor<br>10 W/m <sup>2</sup> * | 3.2%             | 8.7%  | 4.7%                  | 3.7% | 6.7% | 7.7%  |  |

where n is the ideality factor for the solar cell,  $\mathbb{R}_s$  is the series resistance.

# 3.1.2.3 Solar cell technologies for indoor light

For a broad range of applications, solar cell energy harvesters should also be used at indoor light conditions. However, the indoor light spectrum is quite different from the solar cell spectrum at surface of the Earth (AM 1.5 illumination) [101]. A well-performed solar cell under AM 1.5 illumination (100 mW/cm²) may have poor performance under indoor light spectrum and weak light conditions (0.1~10 mW/cm²) because how photons are absorbed by a solar cell depends on the photon energy and the band gap of the semiconductor material of that solar cell. For example, employing monocrystalline silicon (c-Si) solar cells for indoor energy harvesting, researchers found that the indoor efficiency of c-Si is only 10~40% percent of the outdoor efficiency, due to a mismatch of the c-silicon band gap with the indoor fluorescent light spectrum [24, 102-104]. So given our ambition to make ubiquitous energy harvesters, the selection of the thin-film solar cell technology is critical.

From Table 3.1, one can see that particularly c-Si solar cells have relatively poor indoor efficiency. Other technologies, such as a-Si or CIGS solar cells can maintain an efficiency around 7% under indoor light illumination.

Other considerations further narrow down the choice of solar cells integrated on CMOS chips. We discarded CdTe-based cells in view of the environmental concerns with cadmium, which might hamper industrialization (the replacement of lead in solder has been a painstaking process in the

electronics industry [106]). Photo-chemical dye solar cells, as well as the currently known polymer solar cells, have stability concerns over the microsystem's envisaged lifetime [107, 108].

Thus we ended up with a-Si and CIGS solar cells as the most attractive candidates for the monolithic integration. CIGS-based cells have the highest efficiency among the existing (thin-film, mono-junction) types, be it at relatively high process temperatures [109]. Also a-Si solar cells perform very well at indoor-light illumination conditions. The amorphous silicon approach can be expanded to create tandem cells for higher efficiency and higher output voltage. For both CIGS and a-Si technologies, the production equipment is suitable for low-cost monolithic integration on CMOS.

# 3.1.3 CMOS chips selected for monolithic integration

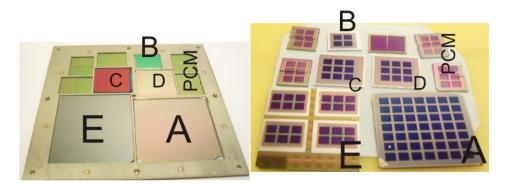

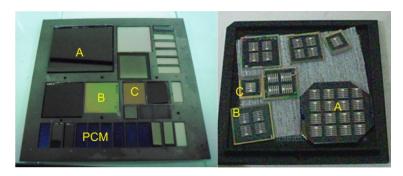

In order to investigate the generic applicability of our monolithic integration approach, we will integrate both the a-Si and CIGS solar cells on CMOS chips of different technologies and with different functionality. Table 3.2 shows the technological specifications of the chosen CMOS chips.

Timepix chip [110] is a mixed-signal CMOS chip processed by 6-metal 0.25 μm technology utilizing shallow trench isolation (STI) and aluminum interconnects. Its active part consists of 256 columns of 256 pixels, and each pixel contains 550 transistors. It is designed to be ball-grid-connected to a semiconductor sensor layer (e.g. CdTe) and also employed in other two-dimensional radiation imaging detectors [111, 112].

The Ringo CMOS chip is a 6-metal 0.18 µm CMOS with Al interconnect, where saw-line process control modules (PCMs) with ring oscillators were characterized.

The Cu-PCM is a 0.13-µm technology CMOS chip with copper interconnects. We used PCMs processed up to the first-metal. Individual MOS capacitors and transistors are available for on-wafer probing in the PCM modules.

The bond pad regions are located at the edge of Timepix chip, those of Ringo chip are located at the dicing-lane. For Cu-PCM, the bond pads are distributed all around the chip close to the single devices, i.e., there is no

Table 3.2: Section of the scalar control of

| sapples (see                     | re¶e∤ | andesk<br>Aspert       | Me <del>l</del> ah 1 | Q5]}  | Inter    | connect      | so                 | urce                      |              | Commer                     | nts             |

|----------------------------------|-------|------------------------|----------------------|-------|----------|--------------|--------------------|---------------------------|--------------|----------------------------|-----------------|

|                                  | ,     | Bu                     | Bulk solar cells     |       |          | Thin-fi      |                    | <del>lm solar cells</del> |              |                            |                 |

| Timepix Light intens             | ity ( | ).25<br><del>c-S</del> | 6                    | GaA   | S        | Al Photochem |                    | ERN<br>Cd7<br>XP          | e            | Functional<br>a-Si         | chip<br>CIGS    |

| Ronagoor<br>AM1.5                | (     | ).18<br>12.5           | % 6                  | 12.49 | <b>%</b> | Cu<br>4.0    | <sub>∕6</sub> Nijı | neggn <sub>7</sub>        |              | ntegrated c<br>7.5%        | ircuit<br>12.9% |

| Cu-Indoor<br>10 W/m <sup>2</sup> | *     | 0.133.29               | 6 6                  | 8.7%  | 0        | Al 4.7       | N<br>IN            | XP<br>1EC <sup>3.79</sup> | Indi<br>6 to | vidual MOS<br>ors and tran | sistors%        |

| Other PCM                        |       | 2                      | 1                    |       |          | Al           |                    | ESA+<br>nolab             | S            | pecified fur               | nction          |

separate region for bond pads. This complicates characterization of the devices after a solar cell is deposited on top, as discussed later on.

The possible damages were listed in Section 1.2.4, we use these three different CMOS chips to monitor the possible influence of the post-process: Different technology generations CMOS chips can give generic information about the integration compatibility on three different levels: single MOS capacitor, MOSFET, single circuits (ring oscillator), to a completed CMOS chips. If there is a metal ion contamination, then flat band voltage of the MOS capacitor will change, if there is plasma charging on the gate oxide, then the gate leakage current of the MOSFET will change. If the process temperature is too high, then the performance of the Timepix will change. If there is a mechanical stress, then solar cells' front-side integration and backside integration will influence CMOS chips differently.

# 3.2 Passivation layers for post-processing

As mentioned in Section 1.2, a passivation layer is needed to prevent possible mechanical and/or electrical damage to the CMOS chips by the post-processing steps before the solar cell integration [19].

Here we present the passivation layer deposition and the electrical measurements of the chip performance before and after post-processing, to evaluate the influence of the passivation step.

Plasma enhanced chemical vapor deposition (PECVD) technique were used to deposit the passivation layers. PECVD of 500 nm  $SiO_2$  and 300 nm  $Si_3N_4$  are for the aforementioned purpose. In order to improve the adhesion between the solar cell and the CMOS chips, PECVD of 250 nm  $SiO_2$ , 300 nm  $Si_3N_4$  and 250 nm  $SiO_2$  stacks may also utilized. After the passivation, the IC chip underwent thermal annealing for 30 minutes at 400 °C in  $N_2$  atmosphere for outgassing the abundant hydrogen incorporated into the passivation layer.

For Cu-PCM chips, in order to retest the performance of the CMOS chip after the solar cell deposition, the passivation layers needs to be removed by wet-etching in BHF. In order to protect Cu bond pads and the low-k dielectric material of the Cu-PCM from BHF, a 100 nm TiW layer is additionally inserted before the deposition of the passivation layers. After the removal of the passivation layer, the TiW layer was etched off by  $H_2O_2$  solution without attacking the Cu bond pads [114].

# 3.2.1 Deposition of Passivation layers

The PECVD technique offers a low-temperature process and a reasonable deposition rate, so we use it to deposit the passivation layers: the SiO<sub>2</sub> was deposited at 300 °C with an RF frequency of 187.5 kHz by Oxford 80 system [115], and a process pressure of 650 mTorr. The Si<sub>3</sub>N<sub>4</sub> was deposited at the same temperature with an RF frequency of 13.6 MHz and 1000 mTorr process pressure. A 500 nm SiO<sub>2</sub> was deposited during 15 minutes, and 300 nm Si<sub>3</sub>N<sub>4</sub> in 15 minutes also. The layer thicknesses were measured by ellipsometer.

The TiW layer was deposited (sputtering) by an Oxford 400 system [115] with a corresponding Ti/W target of 20/80 at%. The magnetron sputtering was done in Ar ambient at 10 mTorr. A 100 nm thick TiW layer was deposited during 130 seconds. The layer thickness was measured by a Dektak surface profiler.

#### 3.2.2 Electrical characterization

Referring to the possible influence of the post-process to the CMOS chip listed in Section 1.2.4 [19], the influence of the passivation layer deposition described in Section 3.2.1 on the CMOS chip may occur due to the high process temperature, the mechanical stress of the added layer, and the hydrogen coming from the PECVD Si<sub>3</sub>N<sub>4</sub> layer.

To clarify this, capacitance-voltage (*C-V*) curves of the MOS capacitor and current-voltage (*I-V*) curves of the MOS transistor have been obtained by a Keithley 4200 SCS system before and after the passivation layer stack realization.

Also to investigate the effect of the high temperature, simple experiments of Timepix chips annealing without any passivation layer in Ar ambient was carried out. The electrical characterizations have been done before and after this annealing experiment.

The results are presented and compared below.

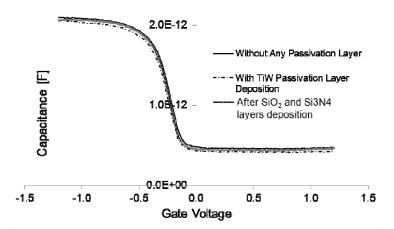

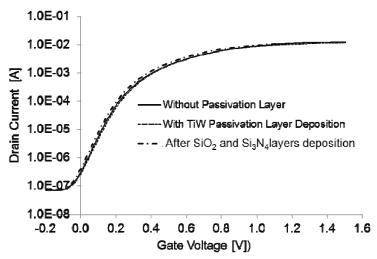

### 3.2.2.1 CV characterization of MOS capacitors on Cu-PCM chips

The MOS capacitor has an area of  $144 \times 10^{-8}$  cm<sup>2</sup> and the oxide thickness is around 2.2 nm. All the capacitance measurements were done at a frequency of 1 MHz.

The CV curves of a MOS capacitor at different stages of processing are shown in Fig. 3.5. The extracted oxide capacitance,  $C_{\rm i}$ , the depletion capacitance,  $C_{\rm D}$ , and the flat band voltage,  $V_{\rm FB}$ , are listed in Table 3.3. The oxide charge of the MOS capacitor is calculated from [96, 116] and is shown in the last column of Table 1.1.

The flat band voltage shifts to the left after the post-processing indicates an increase of positive oxide charge  $\Delta Q$ . The corresponding oxide charge density change is in the order of  $10^{11}/\text{cm}^2$ .

Fig. 3.5. Typical CV curves of a MOS capacitor before and after the passivation layer stack deposition. First, 100 nm thickness of TiW is deposited, then  $500 \text{ nm Si}_{2}$  and  $300 \text{ nm Si}_{3}N_{4}$  were added.

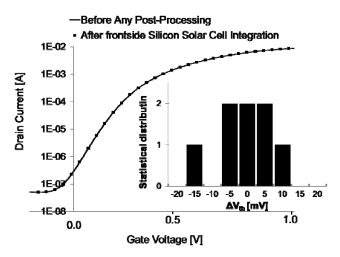

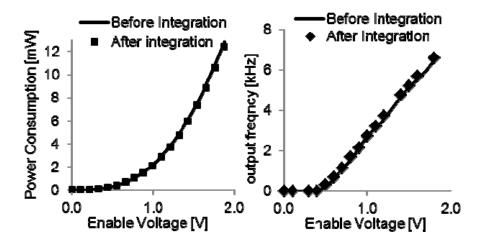

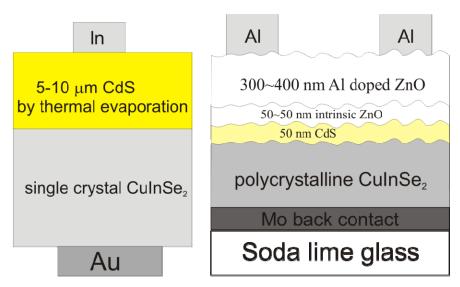

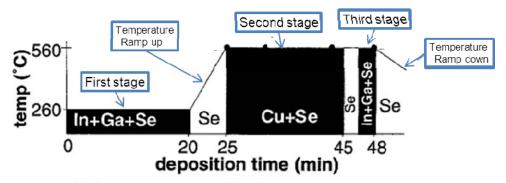

Table 3.4. Typical MOS capacitor parameters before and after post-processing.